半導体開発エンジニアリング

評価技術

私たちは、キオクシアのNAND型フラッシュメモリとUFS / SSDなどのフラッシュストレージ製品に対し、半導体の試験装置(テスタ)を用いた出荷テスト環境を整備して品質を保証しています。多くの製造工程を経て作られる製品の品質をユーザーに対し保証する、とても重要な役目です。理想的な出荷テスト環境の構築を目指して、テスト設計、性能評価、不良品解析を3つの軸にして取り組んでいます。

“製品”品質を守る

- 性能基準に基づく効率的なテスト設計 -製品が満たすべき性能基準や動作条件を明確にし、それに基づいたテストシナリオを設計します。また、フラッシュメモリの大容量化が進んだ影響でテスト時間が長くなる傾向があるため、テストコスト削減に向けた取り組みとして、効率化されたテストパターンを提案します。

“設計”品質を守る

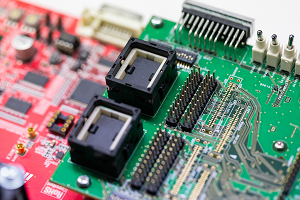

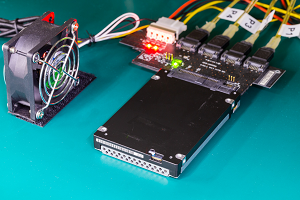

- 実環境に基づく性能評価 -ユーザーが求める動作仕様や性能基準を満たしているかを確認します。実際にユーザーが使用する環境条件に基づいて、周波数特性や消費電力特性などの評価を行い、メモリ製品が設計通りの性能を満たしているかを検証します。

“市場”品質を守る

- 多角的視点に基づく不良品解析 -市場における不良品の解析を行います。解析はテスタによる電気的な分析だけでなく、製造工程や出荷テスト環境で取得したさまざまなデータを用いたトレンド分析も行います。解析結果を出荷テストや製造プロセスにフィードバックすることで、品質の改善につなげています。